# arm Morello Program Overview Mark Inskip, Program Director **Arm Central Engineering** 5 October 2021 © 2021 Arm Limited (or its affiliates)

# Morello Board: Capability Hardware Prototype Platform

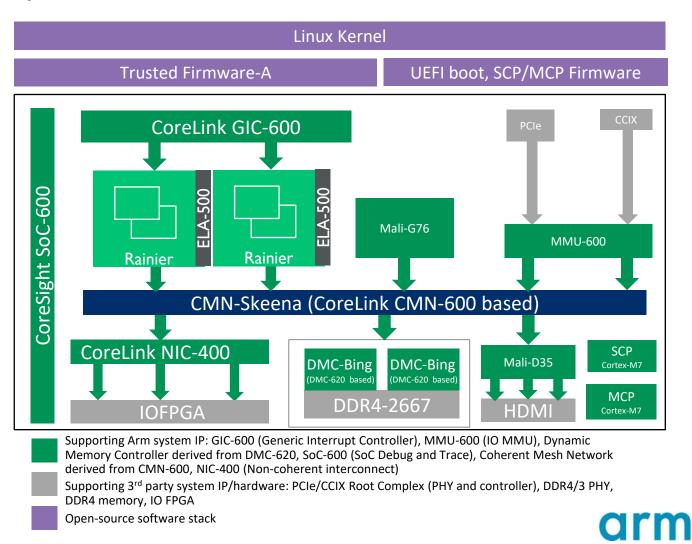

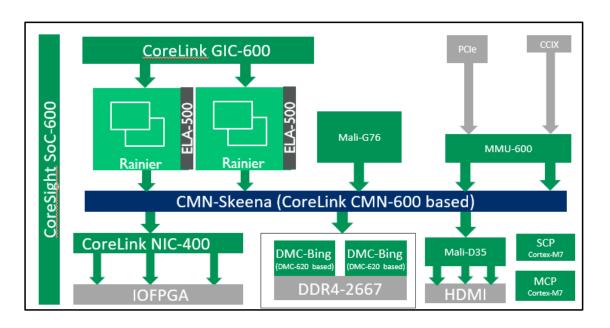

- Silicon implementation of a Capability Hardware CPU Instruction Set Architecture

- Implements Morello Profile for A-class Prototype Architecture

- Two clusters each of two Rainier CPUs

- Interconnect and Memory Controller support for tagged memory

- Two channel DDR4 DRAM interface

- PCle Gen3 and Gen4 x16 interface

- CCIX (Cache Coherent Interconnect for Accelerators) interface

- Mid-range GPU, display processor and HDMI output

- On standard uATX form factor board

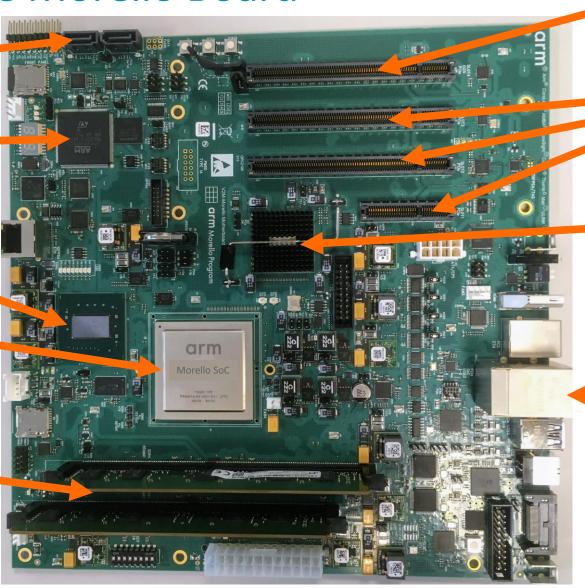

## Overview of the Morello Board

2 x SATA II

Motherboard controller (MCC)

**IOFPGA**

Morello SoC

2 x 72 bit DDR4 RDIMMS, one per channel (16GByte standard config)

1x CCIX compatible PCIe Gen4 x16 slot

3 x Standard PCle Gen3 x16 slot routed as x16, x8, x1

PCle Gen3 Switch

Rear I/O connections

HDMI1.4a output

1Gb Ethernet RJ45

4 x USB3.0

PCC Ethernet

Config USB (inc UARTs)

32 bit TRACE (MIPI 60)

## Overview – Morello Program Timeline

October 2020 January 2022 March 2022 Platforms and Platform model **Development board Volume shipping** milestones AArch64 platform software stacks Hardware bring up General platform Platform ports for firmware. FPGA, SoC, development board. Enablement Operating System support. SBSA compliance testing. Morello Morello architecture support evolving functionality **Architecture** Toolchain, libraries, Kernel development. **Enablement** Prototype userspace examples Linaro and **Ecosystem software access** ecosystem access Infrastructure provision, future engineering support and maintenance

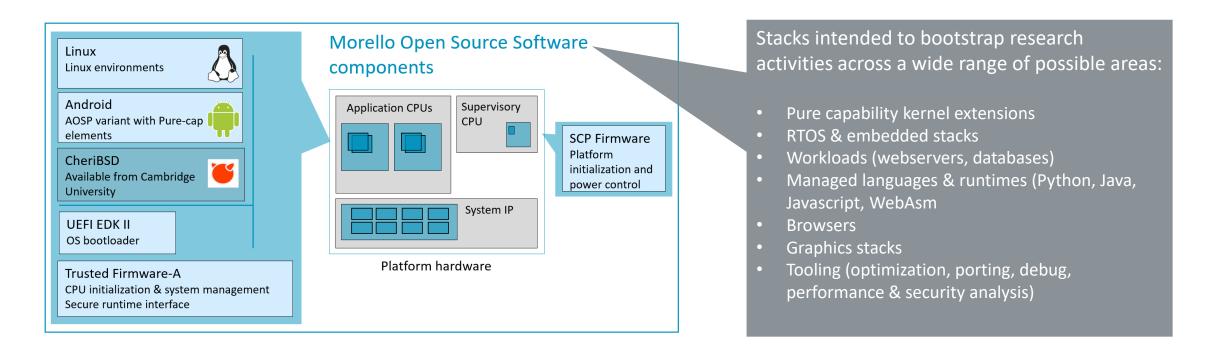

# Morello software ecosystem enablement

#### **Platforms**

https://www.morello-project.org/

#### Software workstreams

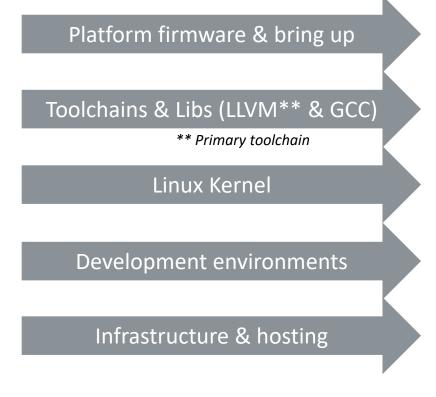

# Software stack foundations to support ecosystem research

#### Collaboration on foundational enablement & feedback is welcome

- Some research activities may be dependent on future work

- Arm's contributions will continue throughout lifetime of Program and functionality will evolve in stages

# Morello hardware development platform – initial support

- Developments boards (Q1 2022 onwards) will be supported by the same software stacks as existing FVP

- Software releases for initial boards may not include mature support, examples:

- Support for DDR & PCIe may not initially be performant

- Satellite peripherals (such as audio and video IPs) may not have driver support

- Secondary features such as power management and network boot may not be available

- Firmware pre-installed on boards should be updated to the latest versions immediately after first validation of boot

#### **Baremetal Enablement**

Evolving releases since Oct 2020

Under development

**Linux Enablement**

#### Firmware stack supports exit at two points

- Post SCP execution: System IP initialized.

Develop from lead processor reset

- Post TF-A execution: Lead Application processor initialized. Runtime services available.

#### Arm Development Studio Morello Edition

- Eclipse based integrated environment for bare-metal configurations

- Supports debug on FVP and (in 2022) development board

#### CheriBSD

- Details presented by University of Cambridge

- Provides a BSD based memory-safe kernel and userspace

- Above common Morello firmware stack

#### Current (nano) headless profile for FVP

- Support for purecap applications & example ports (libjpeg-turbo, logd, BoringSSL, etc) integrated into minimal 64bit AOSP

- Purecap Bionic C library variant (CHERI LLVM/Clang + libshim)

#### Future work (2022 onwards)

- Full Android boot on development board

- Staged Morello Kernel PCuABI features (Q1 on)

- Bionic evolution

- Investigation: Android Runtime + zygote

- Purecap graphics frameworks

#### Initial Proof of Concept (end 2021 for FVP)

- Purecap "Hello world" integrated into standard (64bit) rootfs

- Purecap musl libC (CHERI LLVM/Clang + libshim). Early prototype/limited features.

#### Future work (2022 onwards) \*\*

- Development board support (Q1 22)

- Evolution of CHERI LLVM musl lib C environment: Native compilation on dev board, purecap userspace application ports (Q1 22)

- Morello Kernel PCuABI support (end Q1 on)

- Initial Morello GCC/GlibC environment (Q2 on)

- Proof of concept work to demonstrate a Morello aware Distro framework (Q3 on)

- Purecap graphics frameworks (Q3 on)

<sup>\*\*</sup> uncommitted estimates

## Morello Kernel, C libraries & libshim

#### Morello Linux kernel (Development through 2022)

- Focus on new kernel-user ABI to support purecap userspace software

- Work in associated C libraries (Bionic, Musl, GlibC) both developed against a PCuABI (Pure Capability userspace ABI) specification

- Enabling Linux environments supporting mix of purecap and "COMPAT" 64 bit userspace components

#### Linux and Android built C libraries and libshim

- C libraries initially implemented using concept of a libshim translation layer

- Allows functional development and porting in userspace ahead of mature kernel ABI support

- Does not provide a secure implementation, but allows support for a full set of system calls

#### Aim 1: PCuABI functional support

- Aim: Native support for user-space applications built against the purecap ABI

- Limited set of syscalls, expanded over time.

Allows incremental reduction of reliance on libshim

#### Aim 2: PCuABI memory safety & security

Use of capabilities to improve memory safety at the kernel-user boundary

#### uncommitted estimates

| Initial (lightly modified) ACK – reliant on libshim       | Releases in 2021 |

|-----------------------------------------------------------|------------------|

| Initial Kernel Infrastructure, core purecap functionality | Dev underway     |

| Base 64bit COMPAT (hybrid 64bit & purecap userspace)      |                  |

| Initial PCuABI spec implementation in Kernel              | End Q1 2022      |

| Enforcement of capability metadata (security model)       | Q2 2022 on       |

| Full PCuABI specification implementation                  | Q3 2022 on       |

| Full PCuABI support for Bionic (Android) & musl (Linux)   |                  |

| Full PCuABI support for Glibc (Linux)                     |                  |

## Media Enablement

- Media support for Morello Mali-D35 (Display Processor) and Mali-G76 (GPU) based around Open Source Software

- Mali-D35 supported by existing upstream Kernel driver.

- GPU support will be based on the Open Source Panfrost driver framework for Mali Bifrost GPU architectures

- Timelines

- Initial UI support for the Morello development board will be based on software rendering.

- Panfrost GPU driver platform port (64bit) starts Q1 2022

- purecap ports of graphics libraries will be an ongoing activity through 2022 & beyond

arm

Thank You

Danke

Merci

谢谢

ありがとう

Gracias

Kiitos

감사합니다

धन्यवाद

نکرًا

ধন্যবাদ

תודה

## Morello LLVM & GNU Toolchain timelines

### LLVM (Primary toolchain)

- Ongoing: Regular re-bases to CHERI LLVM.

- CY21Q1 (Done):

- C++ exceptions (static linking).

- CY21Q2 (Done):

- Performance optimisations.

- Descriptor ABI (spec, codegen, LLD, LLDB).

- CY21Q3 (in review):

- C++ exceptions (dynamic linking).

- CY22Q1:

- More extensive public test.

- CY22Q2:

- Code generation for DDC offsetting mode.

#### **GNU Tools**

- CY21Q3 (Done):

- GDB (BET)

- CY21Q3:

- GDB (REL)

- CY21Q4:

- GCC C Lang Support (BET)

- CY22Q1:

- GCC intrinsics

- Glibc (DEV)

- CY22Q2 onward:

- GCC Hybrid cap support

- GCC C++ Language Support